# Implementing Triple-Rate SDI with Spartan-6 FPGA GTP Transceivers

Author: Reed Tidwell

# Summary

The triple-rate serial digital interface (SDI) supporting the SMPTE SD-SDI, HD-SDI, and 3G-SDI standards is widely used in professional broadcast video equipment. SDI interfaces are used in broadcast studios and video production centers to carry uncompressed digital video, along with embedded ancillary data, such as multiple audio channels.

Spartan®-6 FPGA GTP transceivers are well-suited for implementing triple-rate SDI receivers and transmitters. This document describes how to implement triple-rate SDI interfaces using Spartan-6 FPGAs.

# Introduction

The Spartan-6 FPGA triple-rate SDI reference design supports SD-SDI, HD-SDI, and 3G-SDI (both level A and level B). If an application only requires support for a subset of these SDI standards, the triple-rate SDI interface is still used. There is little overhead in the basic triple-rate SDI datapath for the unused SDI standards.

# Differences from Virtex-5 FPGA GTP Transceivers

The GTP transceivers in Spartan-6 devices are similar to the GTP transceivers in Virtex®-5 LXT devices. The differences important to SDI interfaces are described in this section.

Virtex-5 FPGA GTP transceivers in come in GTP\_DUAL tiles, with one PMA PLL (used for reference clock multiplication) shared by the two transmitters and two receivers in the tile. The shared PMA PLL limits the independence of the receivers and transmitters in the tile. Spartan-6 FPGA GTP transceivers also come in GTP\_DUAL tiles; however, Spartan-6 FPGA GTP transceivers have a separate PMA PLL available for each lane (receiver/transmitter pair). This provides two independent clocks that are shared by the transmitters and receivers in the tile. This allows more flexibility in using a tile for both transmitting and receiving; however, it is still not recommended to use a transmitter and receiver with a common clock, unless the reference clock does not change. The receivers should use a different clock from the transmitters because if the transmitter clock changes, the receiver stream incurs errors. It is possible, in Spartan-6 devices, to have transmitters in the same tile transmitting at different bit rates, something that was impossible in Virtex-5 devices because of the single PMA PLL.

The clock recovered by a Virtex-5 FPGA GTP receiver stops if the input serial bitstream stops. This situation often requires using a BUFGMUX to substitute a free-running clock for the recovered clock when it stops, because many video applications cannot tolerate a stoppage in the recovered video clock. The recovered clocks from Spartan-6 FPGA GTP receivers do not stop when the input bitstream stops. This eliminates the need to use BUFGMUXes to swap in a free-running clock.

In GTP\_DUAL tiles of Virtex-5 FPGA GTP transceivers, the reference clock provided to the PMA PLL could be changed dynamically, but only through the DRP port. The reference clock multiplexer for each PMA PLL in the Spartan-6 FPGA GTP transceiver is dynamically controlled by reference clock selection ports, rather than through the DRP.

The Virtex-5 FPGA GTP receiver requires a clock and data recovery (CDR) reset when the input bitstream stops, such as when the SDI cable is unplugged. The preferred method to

<sup>©</sup> Copyright 2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

generate this reset in SDI interfaces is to use the carrier detect signal from the SDI cable equalizer. The Spartan-6 FPGA GTP receiver does not require the carrier detect signal from the SDI cable equalizer to generate a CDR reset when the cable is unplugged.

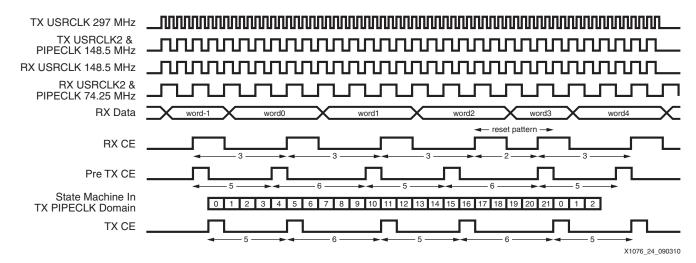

In Virtex-5 FPGA GTP transceivers, the fundamental user clock frequency is at a two word per clock rate. For SDI, this means the user clock rate is 1/20th the serial bit rate. In the Spartan-6 FPGA GTP transceiver, the user clock frequency is one word per clock. For SDI, that means 1/10th the serial bit rate. The GTP transceiver uses a 20-bit parallel interface. Thus, two clocks must be provided to the GTP transceiver: USRCLK at 1/10th the serial bit rate, and USRCLK2 at 1/20th the serial bit rate.

The slowest speed grade, -2, of Spartan-6 devices does not support the 20-bit interface at the speed required for 3G-SDI and oversampled SD-SDI. Therefore, the reference design described in this application note can only be implemented on speed grades of -3 or faster.

## **Supported Video Formats**

The triple-rate SDI receiver and transmitter support the video formats shown in Table 1. The receiver and transmitter do not convert between video and SDI data streams for all video formats. The formats that require conversion between SDI data streams and video using external formatting modules are marked as *External* in the SDI Stream Mapping column. Those that are directly supported are marked with Not required in the SDI Stream Mapping column.

HILL READ

# Table 1: Supported Video Formats

| Interface           | Video Standard        | Sampling Structure/<br>Bit Depth              | Frame/Field Rate (Hz)                                                                        | SDI Stream<br>Mapping |

|---------------------|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------|

| SD-SDI              | PAL                   | 4:2:2 Y'Cb'Cr' 10-bit or 8-bit                | 50                                                                                           | Not required          |

| SMPTE 259-C         | NTSC                  | 4:2:2 Y'Cb'Cr' 10-bit or 8-bit                | 59.94                                                                                        | Not required          |

| HD-SDI<br>SMPTE 292 | SMPTE 274             | 4:2:2 Y'Cb'Cr' 10-bit                         | 1080p: 23.98, 24, 25, 29.97, 30<br>1080i: 50, 59.94, 60<br>1080PsF: 23.98, 24, 25, 29.97, 30 | Not required          |

|                     | SMPTE 296             | 4:2:2 Y'Cb'Cr' 10-bit                         | 720p: 23.98, 24, 25. 29.97, 30, 50, 59.94, 60                                                | Not required          |

|                     | SMPTE 260             | 4:2:2 Y'Cb'Cr' 10-bit                         | 1035i: 59.94, 60                                                                             | Not required          |

|                     | SMPTE 295             | 4:2:2 Y'Cb'Cr' 10-bit                         | 1080i: 50                                                                                    | Not required          |

| 3G-SDI Level A      | SMPTE 274             | 4:2:2 Y'Cb'Cr' 10-bit                         | 1080p: 50, 59.94, 60                                                                         | Not required          |

| SMPTE 425-A         |                       | 4:4:4 or 4:4:4:4 Y'Cb'Cr'<br>or<br>RGB 10-bit | 1080p: 23.98, 24, 25, 29.97, 30<br>1080i: 50, 59.94, 60<br>1080PsF: 23.98, 24, 25, 29.97, 30 | External              |

|                     |                       | 4:4:4 Y'Cb'Cr' or RGB 12-bit                  | 1080p: 23.98, 24, 25, 29.97, 30<br>1080i: 50, 59.94, 60<br>1080PsF: 23.98, 24, 25, 29.97, 30 | External              |

|                     |                       | 4:2:2 Y'Cb'Cr' 12-bit                         | 1080p: 23.98, 24, 25, 29.97, 30<br>1080i: 50, 59.94, 60<br>1080PsF: 23.98, 24, 25, 29.97, 30 | External              |

|                     | SMPTE 296             | 4:4:4 or 4:4:4:4 Y'Cb'Cr'<br>or<br>RGB 10-bit | 720p: 23.98, 24, 25. 29.97, 30, 50, 59.94, 60                                                | External              |

|                     | SMPTE 428-9           | 4:4:4 X'Y'Z' 12-bit                           | 2048 x 1080p: 24                                                                             | External              |

| 3G-SDI Level B      | SMPTE 372             | See Dual-Link HD-SDI SMPTE                    | 372 in this table.                                                                           |                       |

| SMPTE 425-B         | 2 X HD-SDI<br>streams | See HD-SDI SMPTE 292 in this                  | s table.                                                                                     |                       |

| Dual-Link HD-SDI    | SMPTE 274             | 4:2:2 Y'Cb'Cr' 10-bit                         | 1080p: 50, 59.94, 60                                                                         | External              |

| SMPTE 372           |                       | 4:4:4 or 4:4:4:4 Y'Cb'Cr'<br>or<br>RGB 10-bit | 1080p: 23.98, 24, 25, 29.97, 30<br>1080i: 50, 59.94, 60<br>1080PsF: 23.98, 24, 25, 29.97, 30 | External              |

|                     |                       | 4:4:4 Y'Cb'Cr' or RGB 12-bit                  | 1080p: 23.98, 24, 25, 29.97, 30<br>1080i: 50, 59.94, 60<br>1080PsF: 23.98, 24, 25, 29.97, 30 | External              |

|                     |                       | 4:2:2 Y'Cb'Cr' 12-bit                         | 1080p: 23.98, 24, 25, 29.97, 30<br>1080i: 50, 59.94, 60<br>1080PsF: 23.98, 24, 25, 29.97, 30 | External              |

|                     | SMPTE 428-9           | 4:4:4 X'Y'Z' 12-bit                           | 2048 x 1080p: 24                                                                             | External              |

# Triple-Rate SDI Receiver Reference Design

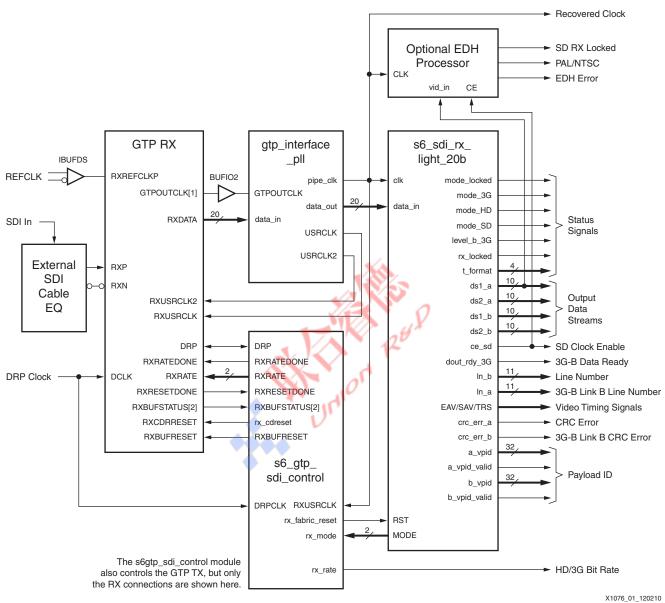

A triple-rate SDI receiver is implemented by an s6\_sdi\_rx\_light\_20b module, combined with a Spartan-6 FPGA GTP receiver and an s6gtp\_sdi\_control module, as shown in Figure 1. Optionally, an EDH processor can be included to provide SD-SDI error checking and lock-detection features.

#### Figure 1: Spartan-6 FPGA GTP Transceiver Triple-Rate SDI Receiver Block Diagram

The triple-rate SDI receiver has these features:

- Uses a 20-bit GTP transceiver interface, supported on -3 and faster Spartan-6 devices

- A single reference clock frequency is required to receive the five supported bit rates:

- 270 Mb/s SD-SDI (SMPTE 259)

- 1.485 Gb/s HD-SDI (SMPTE 292)

- 148.5/1.001 Gb/s HD-SDI (SMPTE 292)

- 2.97 Gb/s 3G-SDI (SMPTE 424)

- 2.97/1.001 Gb/s 3G-SDI (SMPTE 424)

- The receiver has a bit rate detector that can distinguish between the two HD-SDI and two 3G-SDI bit rates. An output signal from the receiver indicates which bit rate is being received.

- The receiver automatically detects the SDI standard of the input signal (3G-SDI, HD-SDI, or SD-SDI) and reports the current SDI mode on an output port.

- The receiver detects and reports the video transport format (e.g., 1080p 30 Hz, 1080i 50 Hz).

- The receiver supports both 3G-SDI level A and level B formats, and automatically detects whether 3G-SDI data streams are level A or B. The 3G-SDI level is reported on an output port.

- The receiver performs CRC error checking for HD-SDI and 3G-SDI modes.

- Optional EDH error checking for SD-SDI is available.

- Line numbers are captured and output from the triple-rate SDI receiver. For 3G-SDI level B

format, line numbers are captured for each of the two HD-SDI streams carried on the

3G-SDI interface.

- SMPTE 352 video payload ID packets are captured for all SDI modes. All captured SMPTE 352 packet data is available on output ports for one or two streams (for those formats that require SMPTE 352 packets in both streams).

- The pipeline clock and the GTP transceiver user clocks are created in the GTP interface module.

- All ancillary data embedded in the SDI data streams is preserved and output from the receiver on the video data stream outputs.

Table 2 describes the I/O ports of the s6\_sdi\_rx\_light\_20b module.

Table 2: I/O Ports of the s6\_sdi\_rx\_light\_20b Module

| Port Name | I/O | Width     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk       | In  | 1         | The user connects this clock input to the pipe_clk output of the gtp_interface_pll module for the GTP RX. The clock frequency is 148.5 MHz (or 148.5/1.001 MHz) for 3G-SDI, and 74.25 MHz (or 74.25/1.001 MHz) for HD-SDI and SD-SDI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| rst       | In  | 1         | This is an asserted High asynchronous reset input. The falling edge of this reset signal must meet the reset recovery time of all flip-flops relative to the next rising edge of clk. Usually, this input can be tied to ground because a reset is not required. After FPGA configuration, this module is in a fully operational mode.                                                                                                                                                                                                                                                                                                                                                                                                   |

| data_in   | In  | 20        | The user connects this port to the data_out_20 port of the ${\tt gtp\_interface\_pll}$ module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| frame_en  | In  | 1         | This input enables the SDI framer function. When this input is High, the framer automatically readjusts the output word alignment to match the alignment of each timing reference signal (TRS), EAV or SAV. Normally, this input should always be High. However, if controlled properly, this input can be used to implement TRS alignment filtering. For example, if the nsp output is connected to the frame_en input, the framer ignores a single misaligned TRS, keeping the existing word alignment until the new word alignment is confirmed by a second matching TRS. It is important to turn off any TRS filtering during the synchronous switching lines by driving the frame_en input High on the synchronous switching lines. |

| ce_sd     | Out | NUM_SD_CE | This output port consists of NUM_SD_CE identical copies of the clock enable signal generated by the SD-SDI data recovery unit in SD-SDI mode. In SD-SDI mode, this output is asserted at a 27 MHz rate. In HD-SDI and 3G-SDI modes, this output is always High.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## Table 2: I/O Ports of the s6\_sdi\_rx\_light\_20b Module (Cont'd)

| Port Name                     | I/O | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mode                          | Out | 2     | <ul> <li>This output port indicates the current SDI mode of the receiver:</li> <li>00 = HD-SDI</li> <li>01 = SD-SDI</li> <li>10 = 3G-SDI</li> <li>When the receiver is not locked, the mode port changes values as the receiver searches for the correct SDI mode. During this time, the mode_locked output is Low. When the receiver detects the correct SDI mode, the mode_locked output goes High.</li> <li>This output port must be connected to the s6gtp_sdi_control module's rx_mode input.</li> </ul>                                                                                                                                 |

| mode_HD<br>mode_SD<br>mode_3G | Out | 1     | These three output ports are decoded versions of the mode port. They are provided for convenience. Unlike the mode port, which changes continuously as the receiver seeks to identify and lock to the incoming signal, these outputs are all forced Low when the receiver is not locked. The mode output matching the current SDI mode of the receiver is High when mode_locked is High.                                                                                                                                                                                                                                                      |

| mode_locked                   | Out | 1     | When this output is Low, the receiver is actively searching for the SDI mode that matches the input data stream. During this time, the mode output port changes frequently. When the receiver locks to the correct SDI mode, the mode_locked output goes High.                                                                                                                                                                                                                                                                                                                                                                                |

| t_format                      | Out | 4     | This output port indicates the video transport timing format of the SDI signal in HD and 3G modes only. Refer to Table 3, page 8 for encoding. The output port is only valid when rx_locked is High. This output port is not valid in SD-SDI mode.                                                                                                                                                                                                                                                                                                                                                                                            |

| rx_locked                     | Out | 1     | This output is High when the receiver is locked to the incoming signal. In HD-SDI and 3G-SDI modes, this output is driven by the transport format detector that generates the t_format output. In SD-SDI mode, this output is identical to the mode_locked signal. Because this output is driven by the transport format detector in HD-SDI and 3G-SDI modes, there can be more than one video frame time of delay from when the receiver is actually locked to the input signal until rx_locked is asserted. During this time, the transport format detector determines the transport format.                                                |

| nsp                           | Out | 1     | When this output is High, the framer has detected a TRS at a new word alignment.<br>If frame_en is High, this output is only asserted briefly. If frame_en is Low, this<br>output remains High until the framer is allowed to readjust to the new TRS<br>alignment (by asserting frame_en High during the occurrence of a TRS).                                                                                                                                                                                                                                                                                                               |

| ln_a                          | Out | 11    | The current line number captured from the LN words of the Y data stream is output<br>on this port. This output is valid in HD-SDI and 3G-SDI modes, but not in SD-SDI<br>mode. In 3G-SDI level B mode, the output value is the line number from the Y data<br>stream of link A or HD-SDI signal 1. For any case where the interface line number<br>is not the same as the picture line number, such as for 1080p 60 Hz carried on<br>3G-SDI level B or dual-link HD-SDI, the output value is the interface line number,<br>not the picture line number.                                                                                       |

| a_vpid                        | Out | 32    | All four user data bytes of the SMPTE 352 packet from data stream 1 are output<br>on this port in this format: most-significant byte to least-significant byte – byte4,<br>byte3, byte2, byte1. This output port is valid only when a_vpid_valid is High. This<br>port is potentially valid in any SDI mode, if there are SMPTE 352 packets<br>embedded in the SDI signal. In 3G-SDI level A mode, the output data is the VPID<br>data captured from data stream 1 (luma). In 3G-SDI level B mode, the output data<br>is the VPID data captured from data stream 1 of link A (dual-link streams) or<br>HD-SDI signal 1 (dual HD-SDI signals). |

| a_vpid_valid                  | Out | 1     | This output is High when a_vpid is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## Table 2: I/O Ports of the s6\_sdi\_rx\_light\_20b Module (Cont'd)

| Port Name    | I/O       | Width            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|--------------|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| b_vpid       | Out       | 32               | All four user data bytes of the SMPTE 352 packet from data stream 2 are output<br>on this port in this format: most-significant byte to least-significant byte – byte4,<br>byte3, byte2, byte1. This output is valid only in 3G-SDI mode and only when<br>b_vpid_valid is High. In 3G-SDI level A mode, the output data is the VPID data<br>captured from data stream 2 (chroma). In 3G-SDI level B mode, the output data<br>the VPID data captured from data stream 1 of link B (dual-link streams) or HD-SDI<br>signal 2 (dual HD-SDI signals). |  |  |

| b_vpid_valid | Out       | 1                | This output is High when b_vpid is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| crc_err_a    | Out       | 1                | This output is asserted High for one sample period when a CRC error is detected<br>on the previous video line. For 3G-SDI level B mode, this output indicates CRC<br>errors on data stream 1 only. There is a second output called crc_err2 that<br>indicates CRC errors on data stream 2 for 3G-SDI level B mode. This output is not<br>valid in SD-SDI mode. The crc_err_a output is asserted High for a single clock<br>cycle when a CRC error is detected.                                                                                    |  |  |

| ds1_a        | Out       | 10               | <ul> <li>The recovered data stream 1 is output on this port. The contents of this data stream are dependent on the SDI mode:</li> <li>SD-SDI: Multiplexed Y/C data stream</li> <li>HD-SDI: Y data stream</li> <li>3G-SDI level A: Data stream 1</li> <li>3G-SDI level B: Data stream 1 of link A or of HD-SDI signal 1</li> </ul>                                                                                                                                                                                                                 |  |  |

| ds2_a        | Out       | 10               | <ul> <li>The recovered data stream 2 is output on this port. The contents of this data stream are dependent on the SDI mode:</li> <li>SD-SDI: Not used</li> <li>HD-SDI: C data stream</li> <li>3G-SDI level A: Data stream 2</li> <li>3G-SDI level B: Data stream 2 of link A or of HD-SDI signal 1</li> </ul>                                                                                                                                                                                                                                    |  |  |

| eav          | Out       | 1                | This output is asserted High for one sample time when the XYZ word of an EAV is present on the data stream output ports.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| sav          | Out       | 1                | This output is asserted High for one sample time when the XYZ word of an SAV is present on the data stream output ports.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| trs          | Out       | 1                | This output is asserted High for four consecutive sample times because all four words of an EAV or SAV are output on the data stream ports.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Outputs Used | Only in 3 | G-SDI Level B Mo | de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| dout_rdy_3G  | Out       | NUM_3G_DRDY      | In 3G-SDI level B mode, the output data rate is 74.25 MHz, but the clock frequency is 148.5 MHz. The dout_rdy_3G outputs are asserted at a 74.25 MHz rate in 3G-SDI level B mode. This output is always High in all other modes, allowing it to be used as a clock enable to downstream modules.                                                                                                                                                                                                                                                  |  |  |

| level_b_3G   | Out       | 1                | In 3G-SDI mode, this output is asserted High when the input signal is level B and Low when it is level A.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| ds1_b        | Out       | 10               | In 3G-SDI mode, the recovered data stream 1 of link B or of HD-SDI signal 2 is output on this port.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| ds2_b        | Out       | 10               | In 3G-SDI mode, the recovered data stream 2 of link B or of HD-SDI signal 2 is output on this port.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| crc_err_b    | Out       | 1                | This output is the CRC error indicator for link B or HD-SDI signal 2. The crc_err_b output is asserted High for a single clock cycle when a CRC error is detected.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| ln_b         | Out       | 11               | This output port is only valid in 3G-SDI level B mode. It outputs the line number for the Y data stream of link B or the HD-SDI signal 2. For any case where the interface line number is not the same as the picture line number, the line number output on this port is the interface line number, not the picture line number.                                                                                                                                                                                                                 |  |  |

Table 3 shows the encoding of the t\_format output port. This port indicates the transport format (not always the same as the picture format) calculated by the receiver by counting words per line and active lines per field or frame. The t\_format port can uniquely identify most video transport formats, but cannot distinguish between transport formats that have identical timing. For example, it cannot differentiate between 1080i 60 Hz and 1080PsF 30 Hz (1080p 30 Hz video carried on a 1080i 60 Hz transport) because there is no difference in the transport timing.

In dual-link HD-SDI and 3G-SDI level B modes, the 1080p 50 and 60 Hz video formats are carried on an interlaced transport. The module reports them as being 1080i 50 Hz and 1080i 60 Hz, respectively. However, in 3G-SDI level A mode, these two video formats are carried progressively and are uniquely identified as 1080p 50 Hz and 1080p 60 Hz (codes 1110 and 1101, respectively).

The transport format detector does not distinguish between frame rates that are 1000 ppm different, such as 1080p 60 Hz and 1080p 59.94 Hz. However, the rx\_rate output of the s6gtp\_sdi\_control module can be used to distinguish between these otherwise identical frame rates.

| t_format | Standard   | Video Format (Frame Rate for p and Field Rate for i)                       |

|----------|------------|----------------------------------------------------------------------------|

| 0000     | SMPTE 260M | 1035i 59.94 Hz and 60 Hz                                                   |

| 0001     | SMPTE 295M | 1080i 50 Hz                                                                |

| 0010     | SMPTE 274M | 1080i 59.94 Hz and 60 Hz<br>1080PsF 29.97 Hz and 30 Hz                     |

| 0011     | SMPTE 274M | 1080i 50 Hz<br>1080PsF 25 Hz                                               |

| 0100     | SMPTE 274M | 1080p 29.97 Hz and 30 Hz<br>1080p 59.94 Hz and 60 Hz (3G-SDI level B only) |

| 0101     | SMPTE 274M | 1080p 25 Hz<br>1080p 50 Hz (3G-SDI level B only)                           |

| 0110     | SMPTE 274M | 1080p 23.98 Hz and 24 Hz                                                   |

| 0111     | SMPTE 296M | 720p 59.94 Hz and 60 Hz                                                    |

| 1000     | SMPTE 274M | 1080PsF 23.98 Hz and 24 Hz                                                 |

| 1001     | SMPTE 296M | 720p 50 Hz                                                                 |

| 1010     | SMPTE 296M | 720p 29.97 Hz and 30 Hz                                                    |

| 1011     | SMPTE 296M | 720p 25 Hz                                                                 |

| 1100     | SMPTE 296M | 720p 23.98 Hz or 24 Hz                                                     |

| 1101     | SMPTE 274M | 1080p 59.94 Hz or 60 Hz (3G-SDI level A only)                              |

| 1110     | SMPTE 274M | 1080p 50 Hz (3G-SDI level A only)                                          |

| 1111     | Reserved   |                                                                            |

Table 3: t\_format Output Port Encoding for the s6\_sdi\_rx\_light\_20b Module

Table 4 describes the parameters (Verilog) or generics (VHDL) of the s6 sdi rx light 20b module.

| Parameter         | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM_SD_CE         | 2       | This parameter specifies the number of identical SD-SDI clock enable output signals provided on the ce_sd port. It specifies the width of the ce_sd port. All bits of the ce_sd port are identical, but separately generate copies. This parameter must never be set to less than 1.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NUM_3G _DRDY      | 2       | This parameter specifies the number of identical 3G-SD level B data ready outputs provided by the module on the dout_rdy_3G port. It specifies the width of the dout_rdy_3G port. All bits of the dout_rdy_3G port are identical, but separately generated copies. This parameter must never be set to less than 1.                                                                                                                                                                                                                                                                                                                                                                                                      |

| ERRCNT_WIDTH      | 4       | This parameter is used by the SDI mode detection<br>function. It specifies the number of bits used in the SDI<br>mode detection error counter. This counter must be wide<br>enough to support counting up to MAX_ERRS_LOCKED<br>and MAX_ERRS_UNLOCKED values.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MAX_ERRS_LOCKED   |         | This parameter is used by the SDI mode detection<br>function. It specifies the maximum number of<br>consecutive lines with errors allowed while the receiver is<br>locked to an SDI signal. When MAX_ERRS_LOCKED<br>consecutive lines with errors are detected, the receiver<br>moves to the unlocked state and begins searching for the<br>new SDI mode. Reducing this value causes the SDI<br>receiver to respond more quickly to an unlocked<br>condition, reducing the time it takes to relock when the<br>SDI input signal changes modes. However, reducing this<br>value can also cause the receiver to be more prone to<br>prematurely moving to an unlocked state during a burst<br>of errors on the SDI signal. |

| MAX_ERRS_UNLOCKED | 2       | This parameter is used by the SDI mode detection<br>function. When the receiver is actively searching for the<br>SDI mode, this parameter specifies the maximum<br>number of consecutive lines with errors allowed before<br>the SDI mode search continues by moving to the next<br>mode. Increasing this value gives the SDI receiver more<br>time to lock to the SDI signal as it tries to lock in each SD<br>mode. However, testing has shown that a value of 2<br>provides adequate lock time while also minimizing the<br>SDI mode detection search time.                                                                                                                                                           |

| Table 4: Parameters for the s6 s | di rx light | 20b Module |

|----------------------------------|-------------|------------|

|----------------------------------|-------------|------------|

## **GTP RX Interface Module**

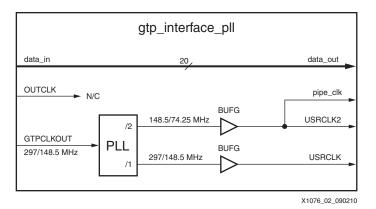

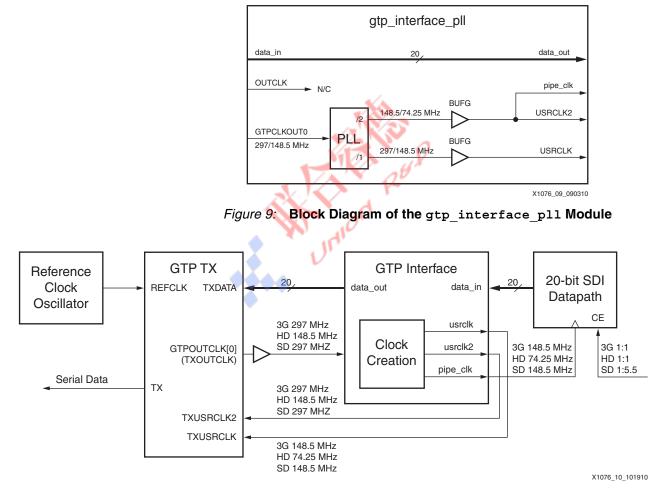

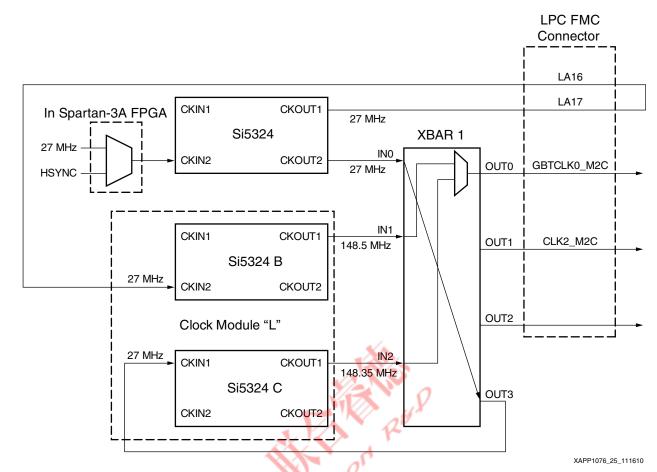

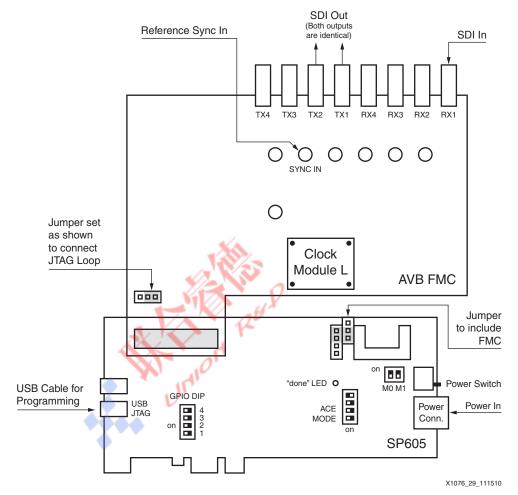

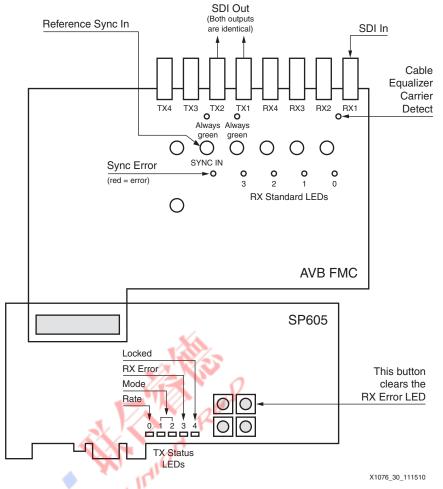

Figure 2 shows a block diagram of the gtp\_interface\_pll module. This module abstracts the clock creation and buffering so that alternate clock creation and distribution schemes can be employed by the user, if desired. The 20-bit data is routed through this module to facilitate synchronization between clock domains, if it is required for the alternate clocking schemes.

The module creates the two synchronized user clocks required for interfacing to the GTP transceiver: usrclk and usrclk2. Pipe\_clk is identical to usrclk2.

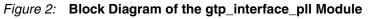

The input clock is the RX recovered clock from the GTP transceiver. Table 5 describes the inputs and outputs of this module. Figure 3 shows the gtp\_interface\_pll module in the context of a triple-rate SDI receiver. This module is also used for the GTP transmitter, but it requires a separate instance, and the usage and clock frequencies are different (see GTP TX Interface Module, page 22).

Figure 3: GTP Interface Module in RX Context

| Table 5: | I/O Ports | of the gtp_ | _interface_ | _pll Module |

|----------|-----------|-------------|-------------|-------------|

| Port Name    | I/O | Width | Description                                                                                                                                                                                                      |

|--------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| outclk       | In  | 1     | Not used. Output clocks using dedicated clock routing come through gtpclkout.                                                                                                                                    |

| gtpoutclk    | In  | 1     | PLL input clock on dedicated clock routing. Nominally, 297 MHz for 3G-SDI and 148.5 MHz for HD-SDI and SD-SDI. This should be connected to the GTPOUTCLK[1] port of the GTP transceiver through a BUFIO2 buffer. |

| pll_reset_in | In  | 1     | Asynchronous PLL reset.<br>1 = Reset PLL.<br>0 = Do not reset PLL.                                                                                                                                               |

| data_in      | In  | 20    | 20-bit input data. This should be connected to the RXDATA port of the GTP transceiver.                                                                                                                           |

| usrclk       | Out | 1     | Output user clock at one times the input clock rate. Nominally, 297 MHz for 3G-SDI, and 148.5 MHz for HD-SDI and SD-SDI. This is used to drive the USRCLK input of the GTP transceiver.                          |

| usrclk2      | Out | 1     | Output user clock at one-half times the input clock rate. Nominally, 148.5 MHz for 3G-SDI, and 74.25 MHz for HD-SDI and SD-SDI. This output drives the USRCLK2 input of the GTP transceiver.                     |

| pipe_clk     | Out | 1     | Pipeline clock for downstream pixel processing. This must be at the same frequency as usrclk2. In the reference design, it is the same clock.                                                                    |

www.xilinx.com

| Port Name      | I/O | Width | Description                                                                                     |

|----------------|-----|-------|-------------------------------------------------------------------------------------------------|

| data_out       | Out | 20    | 20-bit output data. This should be connected to the data_in port of the S6_sdi_rx_light module. |

| pll_locked_out | Out | 1     | Locked flag from the PLL.<br>1 = Locked.<br>0 = Unlocked.                                       |

#### Table 5: I/O Ports of the gtp\_interface\_pll Module (Cont'd)

### **Operation of the Triple-Rate SDI Receiver in the Various SDI Modes**

The triple-rate SDI receiver automatically determines the standard of the incoming SDI mode (SD-SDI, HD-SDI, 3G-SDI level A, or 3G-SDI level B). It does this by sequentially trying to lock to each SDI mode until it finds the correct SDI mode. When locked to the correct SDI mode, the receiver configures itself for correct operation in that mode. The recovered clock frequency and the number and data rate of the output data streams depend on the SDI mode.

#### Triple-Rate SDI Clocking

The GTP receiver's CDR unit requires a reference clock, which can be either 74.25 MHz or 74.25/1.001 MHz. Some integer multiples of these frequencies are also supported. In particular, 148.5 MHz and 148.5/1.001 MHz are also commonly used. Only a single reference clock frequency is required to support SD-SDI at 270 Mb/s, HD-SDI at both bit rates, and 3G-SDI at both bit rates. The frequency of the reference clock should not change. Any change in the reference clock frequency requires resetting the GTP RX, including the RX PMA PLL.

The GTP receiver recovers a clock in 3G-SDI and HD-SDI modes, but not in SD-SDI mode. The recovered clock from the GTP transceiver is output on bit 1 of the GTPOUTCLK port. This port is connected to dedicated clock resources and is used in place of RXRECCLK to carry the recovered clock. The frequency of the recovered clock depends on the current SDI mode of the receiver. In HD-SDI mode, it is 148.5 MHz or 148.5/1.001 MHz. In 3G-SDI mode, it is 297 MHz or 297/1.001 MHz. In SD-SDI mode, the CDR unit is locked to the reference clock and GTPOUTCLK[1] is either 148.5 MHz or 148.5/1.001 MHz, depending on the frequency of the reference clock.

The GTPOUTCLK[1] output of the GTP receiver usually should be buffered by a BUFIO2 buffer. The output of this clock buffer drives the gtpoutclk1 input of the gtp\_interface\_pl1 module. The gtp\_interface\_pl1 module is shown in Figure 2. This module creates two synchronous clocks from the RX recovered clock by dividing the clock by 1 and 2 using a PLL. These clocks are buffered by global clock buffers. The usrclk output is at the recovered clock rate. The usrclk2 output is at one-half the recovered clock rate. These two clocks are required by the GTP RX interface. They must be synchronous with each other and with the data going into the GTP interface. The pipe\_clk is identical to usrclk2 at one-half the recovered clock, and thus can be used to clock the 20-bit s6\_sdi\_rx\_light\_20b module and any other downstream logic. It can also be used to drive any additional downstream modules that need to be clocked by the recovered clock.

Internally, most of the logic in the  $s6\_sdi\_rx\_light\_20b$  module runs at the pipe clock frequency for HD-SDI and 3G-SDI (some portions run at half the pipe clock frequency in 3G-SDI level B mode). For SD-SDI, the internal data rate is 27 MHz. Clock enables are used in the  $s6\_sdi\_rx\_light\_20b$  module to run the various sections at the proper rates when the data rate is different from the clock frequency.

The  $s6\_sdi\_rx\_light\_20b$  module also supplies one or more copies of the SD-SDI clock enable on the ce\_sd output port. These clock enables can be used, in conjunction with the recovered clock, to clock logic downstream from the  $s6\_sdi\_rx\_light\_20b$  module at the 27 MHz SD-SDI data rate. The NUM\_SD\_CE parameter/generic specifies the number of identical copies of ce\_sd output by the module. NUM\_SD\_CE must never be set to less than 1. The source of the ce\_sd clock enable signal is the SD-SDI data recovery unit (DRU) located inside the  $s6\_sdi\_rx\_light\_20b$  module. Typically, the cadence of a ce\_sd signal is 3/3/3/2 cycles of the clock. However, the cadence varies occasionally to make up for differences between the actual recovered data rate and the frequency of the reference clock. In all modes except SD-SDI, ce\_sd is always High.

The s6\_sdi\_rx\_light\_20b module also outputs a dout\_rdy\_3G data ready signal. In 3G-SDI level B mode, dout\_rdy\_3G toggles at half the recovered clock frequency because the output data rate is 74.25 MHz and the clock frequency is 148.5 MHz. In all modes except 3G-SDI level B, dout\_rdy\_3G is always High. The NUM\_3G\_DRDY parameter/generic specifies the number of identical copies of the dout\_rdy\_3G signal output by the module. NUM\_3G\_DRDY should never be set to less than 1.

The ce\_sd clock enable signals can be used as clock enables to those datapaths that only operate at the SD-SDI data rate, such as the optional SD-SDI EDH processor. The ce\_sd signal is always High when not in SD-SDI mode. The dout\_rdy\_3G signal can be used as a clock enable to those datapaths that operate in HD-SDI and 3G-SDI modes, but not in SD-SDI mode. In SD-SDI mode, dout\_rdy\_3G is always High. If a datapath must operate correctly in all three SDI modes, it should use a clock enable that is the AND of a ce\_sd signal and a dout\_rdy\_3G signal.

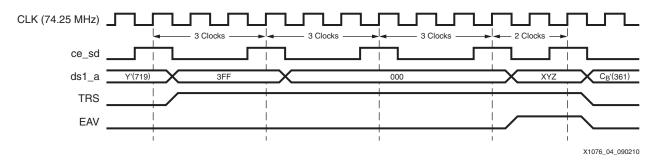

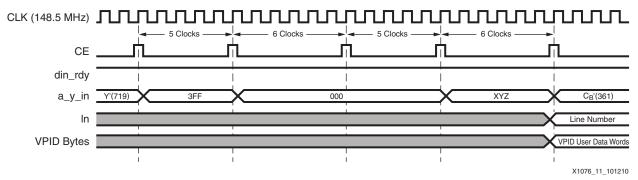

#### **SD-SDI Output Timing**

When the triple-rate SDI receiver operates in SD-SDI mode, the frequency of rxpipeclk is 74.25 MHz or 74.25/1.001 MHz, depending on the reference clock frequency. The recovered SD-SDI data stream is output on the ds1\_a port with the Y and C components interleaved at a 27 MHz data rate. The timing signals trs, eav, and sav are valid.

In SD-SDI mode, pipe\_clk is not a recovered clock because the GTP receiver is locked to the reference clock and asynchronously samples the input bitstream. pipe\_clk is, therefore, an exact multiple of the reference clock supplied to the GTP receiver.

A data recovery unit (DRU) in the s6\_sdi\_rx\_light\_20b module recovers the actual data stream from the oversampled data. The DRU provides a data ready signal that is asserted when it has a 10-bit data word ready. The s6\_sdi\_rx\_light\_20b module outputs this data ready signal on the ce\_sd output. On average, this output is asserted once every 2.75 clock cycles by using a 3/3/2 clock cycle cadence. The output cadence is occasionally altered when the DRU needs to catch up to the actual data rate. This occurs because the GTP transceiver reference clock is a local clock and is asynchronous to the actual timing of the incoming SD-SDI bitstream. High amounts of jitter on the SD-SDI can also cause the cadence to vary.

Figure 4 shows the timing of the SD video and timing signals output by the s6\_sdi\_rx\_light\_20b module. The outputs only change on the rising edge of clk when ce\_sd is High. The timing of the EAV sequence is shown. The sav output signal has the same timing as the eav signal except that it is asserted during SAV sequences.

Figure 4: SD-SDI RX Timing Diagram

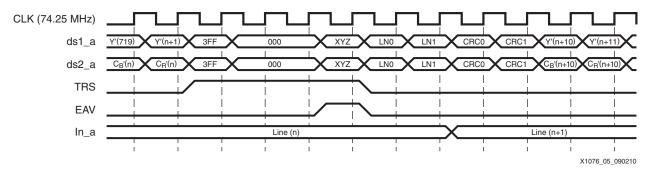

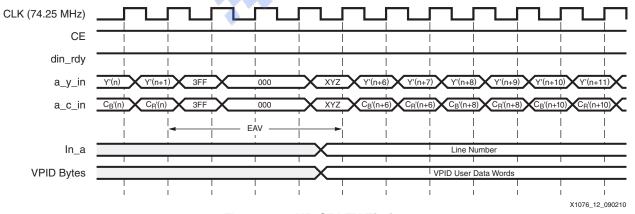

#### **HD-SDI Output Timing**

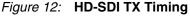

When the triple-rate SDI receiver operates in HD-SDI mode, pipe\_clk is based on a true recovered clock and runs at 74.25 MHz or 74.25/1.001 MHz, depending on the HD-SDI bit rate. The Y and C data streams of the HD-SDI signal are output on the ds1\_a and ds2\_a ports, respectively, along with the timing signals trs, eav, and sav. The line number is output on the In\_a port. In HD-SDI mode, the line number changes during the CRC0 word. Figure 5 shows the timing of the HD-SDI outputs.

Figure 5: HD-SDI RX Timing Diagram

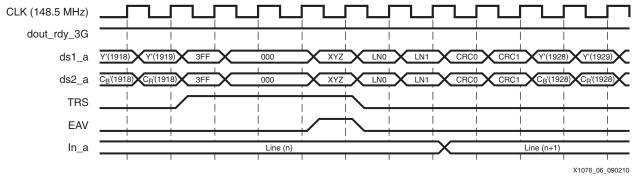

#### **3G-SDI Level A Output Timing**

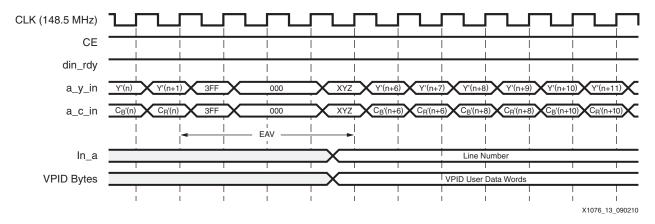

When the triple-rate SDI receiver operates in 3G-SDI level A mode, the frequency of pipe\_clk is 148.5 MHz or 148.5/1.001 MHz, depending on the 3G-SDI bit rate.

Figure 6 shows the output timing of the s6\_sdi\_rx\_light\_20b module when receiving a 1080p 50, 59.94, or 60 Hz signal in 3G-SDI level A mode. These video formats do not require further unpacking of the data streams, because ds1\_a carries the luma component and ds2\_a carries the multiplexed chroma components.

Other video formats, such as 4:4:4 10-bit or 12-bit, have identical timing to that shown in Figure 6, but the video samples are packed as specified by the SMPTE 425 so that it takes two consecutive words on each data stream to carry a single video sample. The  $s_{6\_sdi\_rx\_light\_20b}$  module does not unpack these other video formats, but outputs the two data streams exactly as described in the 3G-SDI level A data stream mapping sections of SMPTE 425.

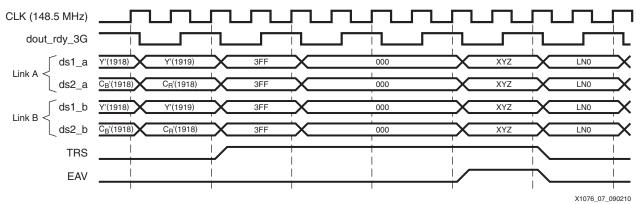

#### **3G-SDI Level B Output Timing**

When the triple-rate SDI receiver operates in 3G-SDI level B mode, the frequency of pipe\_clk is 148.5 MHz or 148.5/1.001 MHz, depending on the 3G-SDI bit rate. However, in this mode, there are four 10-bit data streams output by the  $s6\_sdi\_rx\_light\_20b$  module. The data rate of these data streams is half the frequency of pipe\_clk, therefore, the dout\_rdy\_3G signal is asserted every other clock cycle and acts as a clock enable.

Figure 7 shows the output timing of the s6\_sdi\_rx\_light\_20b module when receiving a 3G-SDI level B signal.

Both line number output ports are active. When the level B signal is transporting SMPTE 372 dual-link data streams, the values on both In\_a and In\_b are identical and indicate the interface line number, not the picture line number. When the level B signal is transporting two independent HD-SDI signals, the two line number values are not necessarily the same, depending on whether the two HD-SDI signals are frame locked or not. The In\_a and In\_b ports, not shown in Figure 7, change at the same relative position as they do for 3G-SDI level A and HD-SDI, as the CRC0 word is output on the data streams.

When the 3G-SDI level B signal carries SMPTE 372 dual-link data streams, the link A data streams are output on ds1\_a and ds2\_a and the link B data streams are output on ds1\_b and ds2\_b. These four links carry video mapped as required by SMPTE 372. The  $s6\_sdi\_rx\_light\_20b$  module does not unpack the data streams into video, but outputs them as SMPTE 372 data streams.

When the 3G-SDI level B signal carries two independent HD-SDI streams, the first HD-SDI stream is output with the luma component on ds1\_a and the multiplexed chroma components on ds2\_a. The second HD-SDI stream is output with the luma component on ds1\_b and the multiplexed chroma component on ds2\_b. These two HD-SDI streams are horizontally synchronized so that their EAVs and SAVs always line up exactly, therefore there is only a single set of eav, sav, and trs timing signals.

# Other Triple-Rate SDI RX Design Considerations

To incorporate the triple-rate receiver into a complete system, the designer should take into account some additional considerations. This section describes those considerations.

#### HD-SDI and 3G-SDI Bit Rate Detection

The s6gtp\_sdi\_control module contains a bit rate detector. The rx\_rate output of the s6gtp\_sdi\_control module is 0 when the incoming bit rate is 1.485 Gb/s or 2.97 Gb/s. It is 1 when the incoming bit rate is 1.485/1.001 Gb/s or 2.97/1.001 Gb/s. The bit rate detector depends on a known constant frequency clock supplied to the s6gtp\_sdi\_control module on its dclk port. Refer to SDI GTP Transceiver Control Module, page 32 for a detailed description of this module.

#### **Dual-Link HD-SDI**

To implement a dual-link HD-SDI receiver, two triple-rate SDI receivers are paired together with one receiving link A and the other receiving link B. Typically, the received data streams for the two links are skewed, so the skew must be removed. Next, the data streams can be unpacked into video streams, if desired.

Deskewing the data streams involves watching the EAV or SAV signals from each link and delaying the data streams of the link whose EAV becomes asserted first by an appropriate amount to match the timing of the other link. The Spartan-6 FPGA SRL elements make perfect delay devices for implementing this deskew function.

#### Processing Embedded Audio and Other Ancillary Data

The data streams that are output from the triple-rate SDI receiver always have all ancillary data intact, including embedded audio packets. Modules designed to process ancillary data can be connected to the data streams, clock enables, and other timing signals output by the triple-rate SDI receiver.

#### **SMPTE 352 Video Payload ID Packets**

The triple-rate SDI receiver module captures SMPTE 352 packets present in the data streams for all SDI modes. For SD-SDI and HD-SDI, the four data bytes of the SMPTE 352 packet are output on the a\_vpid port. The a\_vpid\_valid port indicates when valid SMPTE 352 packets have been captured. This output has some hysteresis so that SMPTE 352 packets can be missing from a few fields or frames before the valid signal is negated. During the time that the valid output is asserted and new SMPTE 352 packets are not found, the data from the last valid SMPTE 352 packet received is output on the a\_vpid port.

The 3G-SDI standard requires SMPTE 352 packets in both data streams. The triple-rate SDI receiver captures the SMPTE 352 packets from both streams, outputting the data from the packet in data stream 1 on a\_vpid and the data from the packet in data stream 2 on b\_vpid. The module also provides individual a\_vpid\_valid and b\_vpid\_valid outputs.

#### SD-SDI EDH Error Detection

The triple-rate SDI receiver detects CRC errors in HD-SDI and 3G-SDI modes, but it does not contain an EDH error checker. However, either of the two EDH processors described in Chapters 6 and 7 of *Audio/Video Connectivity Solutions for Virtex-II Pro and Virtex-4 FPGAs* [Ref 1] can be connected downstream from the s6\_sdi\_rx\_light\_20b module to check the SD-SDI data stream for EDH errors.

#### SD-SDI Data Recovery Unit

The triple-rate SDI receiver uses a DRU to recover the SD-SDI data. This DRU is based on the digital PLL data recovery design described in *Dynamically Programmable DRU for High-Speed Serial I/O* [Ref 2], but has been optimized for SD-SDI and ported to the Spartan-6 FPGA. This SD-SDI DRU has been optimized for use with 5.5X oversampled 270 Mb/s data. By optimizing the DRU specifically for SD-SDI, it is much smaller than the general-purpose implementation of the DRU. The SD-SDI DRU has also been optimized so that the reference clock used for SD-SDI reception can be either 74.25 MHz or 74.25/1.001 MHz.

#### **Electrical Interface**

The GTP receiver must be connected to the SDI connector through an SDI cable equalizer. The equalizer serves two purposes. It equalizes the SDI signal to compensate for signal distortion and attenuation, and it converts the single-ended 75 $\Omega$  SDI signal to a differential signal compatible with the GTP receiver input. Most, if not all, SDI cable equalizers currently available do not have a common mode output directly compatible with the Spartan-6 FPGA GTP transceiver inputs. Therefore AC coupling is required to shift the common mode voltage of the signal as it enters the GTP receiver. The GTP receiver has built-in AC coupling, but these internal capacitors are not adequate to support the long run lengths of the SDI signals. The internal AC coupling must be bypassed, and external AC coupling capacitors must be used. The value of these external capacitors is usually about 4.7  $\mu$ F. Nothing else needs to be done to set the common mode voltage because the GTP receiver provides a correct termination voltage to set the common mode voltage on its inputs.

# Triple-Rate SDI<br/>Transmitter<br/>Reference<br/>DesignThe Spartan-6 FPGA SDI transmitter provides the basic operations necessary to support<br/>SD-SDI, HD-SDI, dual-link HD-SDI, and 3G-SDI transmission. The transmitter does not<br/>perform video mapping for 3G-SDI or dual-link HD-SDI. Video formats that require mapping<br/>must be mapped into SDI data streams prior to the triple-rate SDI TX module. These video<br/>formats include those in Table 1 marked "external" in the "SDI Stream Mapping column: 3G-SDI<br/>level A formats except 1080p 50 Hz, 59.94 Hz, and 60 Hz, all 3G-SDI level B formats, and all<br/>dual-link HD-SDI formats.

The Spartan-6 FPGA GTP transceiver triple-rate SDI transmitter has these features:

- A 20-bit GTP interface, supported on -3 and faster Spartan-6 devices.

- Only two reference clock frequencies are required to support all SDI modes:

- 148.5 MHz for SD-SDI at 270 Mb/s, HD-SDI at 1.485 Gb/s, and 3G-SDI at 2.97 Gb/s.

- 148.5/1.001 MHz for HD-SDI at 1.485/1.001 Gb/s and 3G-SDI at 2.97/1.001 Gb/s.

- Direct support for 3G-SDI level A transmission of 1080p 50 Hz, 59.94 Hz, and 60 Hz video.

- Transmission of preformatted dual-link HD-SDI streams via either dual-link HD-SDI or 3G-SDI level B formats.

- With the addition of a 3G-SDI level A mapping module, supports all 3G-SDI level A compatible video formats.

- Direct support for transmission of two independent HD-SDI streams via 3G-SDI level B format.

- EDH packets generated and updated for SD-SDI mode.

- CRC values can be generated and inserted for HD-SDI and 3G-SDI modes.

- Line number words inserted for HD-SDI and 3G-SDI modes.

- SMPTE 352M video payload ID packets can be generated and inserted in all SDI modes.

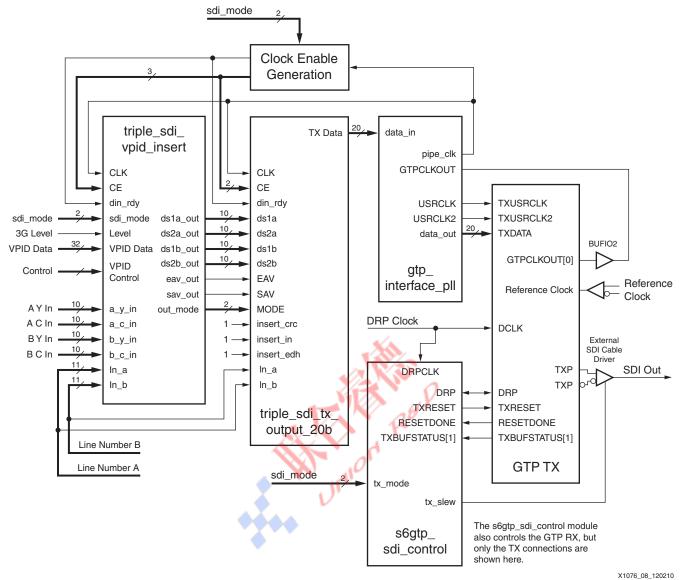

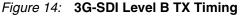

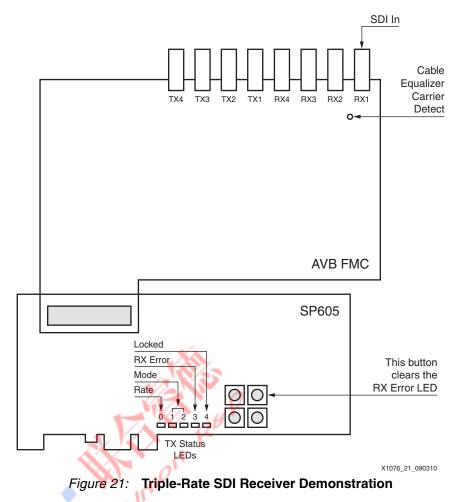

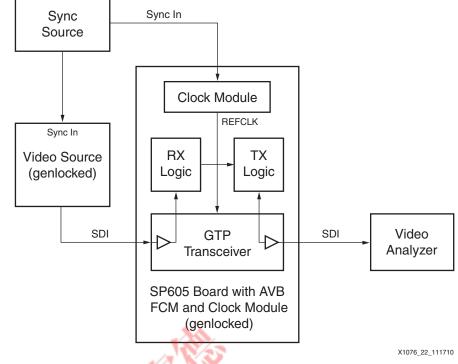

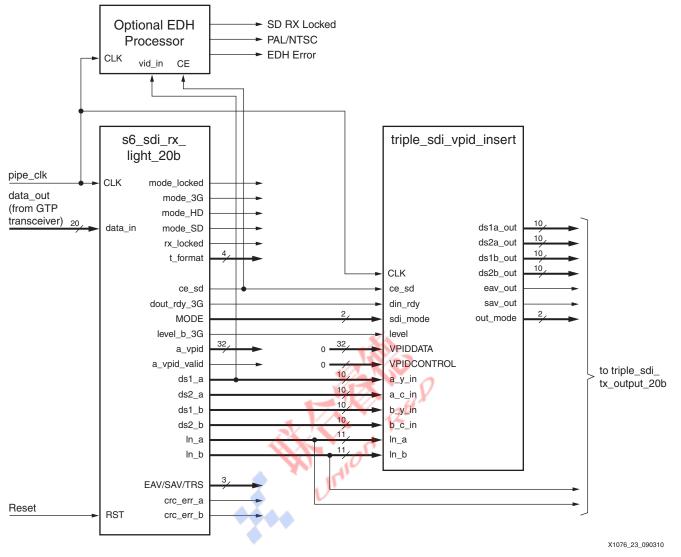

A block diagram of the Spartan-6 FPGA GTP Transceiver triple-rate SDI transmitter is shown in Figure 8.

The transmitter datapath consists of three modules: triple\_sdi\_vpid\_insert, triple\_sdi\_tx\_output\_20b, and gtp\_interface\_pll. These three modules, combined with the GTP transceiver and the s6gtp\_sdi\_control module, form the triple-rate SDI transmitter design. One s6gtp\_sdi\_control module is required per GTP transceiver (RX/TX pair). If both the RX and the TX in a GTP transceiver are used for SDI, only one s6gtp\_sdi\_control module is required for that transceiver. Figure 8 only shows the transmitter connections of the GTP transceiver wrapper and the s6gtp\_sdi\_control module.

# Figure 8: Spartan-6 FPGA GTP Transceiver Triple-Rate SDI Transmitter Block Diagram

# **Triple-Rate SDI Transmitter Datapath Modules**

The triple-rate SDI transmitter datapath consists of two datapath modules, the triple\_sdi\_vpid\_insert module, which inserts SMPTE 352 video payload ID packets into the data streams, and the triple\_sdi\_tx\_output\_20b module, which creates a final output data stream suitable for input to the TXDATA port of the GTP transmitter.

# **Triple-Rate SDI VPID Insert Module**

Table 6 describes the ports of the triple\_sdi\_vpid\_insert module. This module is the front-end of the triple-rate SDI transmitter. Its main function is to insert SMPTE 352 video payload ID packets into the data streams, but it also provides some additional functions required by the triple\_sdi\_tx\_output\_20b module, such as detecting and identifying EAV and SAV sequences and generating the out\_mode signal that connects to the mode port of the output module. Even if SMPTE 352 packets do not need to be inserted in a particular application (these packets are required for 3G-SDI and dual-link HD-SDI modes), the triple\_sdi\_vpid\_insert module is still required to perform these additional functions. If the triple\_sdi\_vpid\_insert module's enable input port is wired Low, the actual

SMPTE 352 packet generation and insertion logic is optimized out of the design, and only the additional required functions of the module are retained by the synthesizer.

| Table | 6: I | /0 | Ports of | the | triple | sdi | vpid | insert Module | ļ |

|-------|------|----|----------|-----|--------|-----|------|---------------|---|

|-------|------|----|----------|-----|--------|-----|------|---------------|---|

| Port Name | I/O | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| clk       | In  | 1     | This clock input must be driven by the pipe_clk. It must have a frequency of 74.25 MHz or 74.25/1.001 MHz for HD-SDI, 148.5 MHz or 148.5/1.001 MHz for 3G-SDI, and 148.5 MHz for SD-SDI modes.                                                                                                                                                                                                                                                                    |  |  |  |

| се        | In  | 1     | The clock enable must be asserted at a 27 MHz rate for SD-SDI mode (with a mandatory 5/6/5/6 clock cycle cadence). For all other SDI modes, the clock enable is always High.                                                                                                                                                                                                                                                                                      |  |  |  |

| din_rdy   | In  | 1     | For SD-SDI, HD-SDI, and level A 3G-SDI modes, this input must be kept High at all times. For level B 3G-SDI mode, this input must be asserted every other clock cycle.                                                                                                                                                                                                                                                                                            |  |  |  |

| rst       | In  | 1     | This asynchronous reset input resets the module when High. The falling edge of this reset signal must meet the reset recovery time of all flip-flops relative to the next rising edge of clk.                                                                                                                                                                                                                                                                     |  |  |  |

| sdi_mode  | In  | 1     | <ul> <li>This input port is used to select the transmitter SDI mode:</li> <li>00 = HD-SDI (including dual-link HD-SDI)</li> <li>01 = SD-SDI</li> <li>10 = 3G-SDI</li> <li>11 = Invalid</li> </ul>                                                                                                                                                                                                                                                                 |  |  |  |

| level     | In  | 1     | In 3G-SDI mode, this input determines whether the module inserts SMPTE 352 packets for level A (level = Low) or for level B (level = High). Because these two 3G-SDI levels have different requirements for placement of SMPTE 352 packets, this input must be properly controlled, otherwise the data streams generated by the module are not legal.                                                                                                             |  |  |  |

| enable    | In  | 1     | When this input is High, SMPTE 352 packets are inserted into the data streams, otherwise the packets are not inserted. SMPTE 352 packets are mandatory in 3G-SDI and dual-link HD-SDI modes.                                                                                                                                                                                                                                                                      |  |  |  |

| overwrite | In  | 1     | If this input is High, SMPTE 352 packets already present in the data streams are overwritten.<br>If this input is Low, existing SMPTE 352 packets are not overwritten. When transporting<br>SMPTE 372 dual-link data streams on a 3G-SDI level B interface, existing SMPTE 352 packets<br>in the data streams must be updated to indicate that the interface is 3G-SDI rather than<br>HD-SDI mode. This module updates these packets only when overwrite is High. |  |  |  |

| byte1     | In  | 8     | This value is inserted as the first user data word of the SMPTE 352 packet. It must be valid during the entire HANC interval.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| byte2     | In  | 8     | This value is inserted as the second user data word of the SMPTE 352 packet. It must be valid during the entire HANC interval.                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| byte3     | In  | 8     | This value is inserted as the third user data word of the SMPTE 352 packet. It must be valid during the entire HANC interval.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| byte4a    | In  | 8     | This value is inserted as the fourth user data word of the SMPTE 352 packet. This word is u for the SMPTE 352 packets inserted into SD-SDI, HD-SDI, and 3G-SDI level A data strea For 3G-SDI level B and dual-link HD-SDI modes, this value is used for the SMPTE 352 packets inserted into Y channel of link A only. This input must be valid during the entire HANC inte                                                                                        |  |  |  |

| byte4b    | In  | 8     | This value is inserted as the fourth user data word of SMPTE 352 packets inserted in the Y channel of link B for 3G-SDI level B and dual-link HD-SDI modes only. This input value is not used for SD-SDI, HD-SDI, or 3G-SDI level A modes. This input must be valid during the entire HANC interval.                                                                                                                                                              |  |  |  |

# Table 6: I/O Ports of the triple\_sdi\_vpid\_insert Module (Cont'd)

| Port Name  | I/O | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ln_a       | In  | 11    | The current line number must be provided to the module through this port if SMPTE 352 packet insertion is enabled. If SMPTE 352 packet insertion is disabled in a particular SDI mode, SD-SDI for example, valid line numbers do not need to be supplied on this port in that SDI mode.                                                                                                                                                                                                                              |

|            |     |       | SD-SDI only uses 10-bit line numbers, so bit 10 of the port must be 0 in SD-SDI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |     |       | The line number must be valid at least one clock cycle before the start of the HANC space (by the XYZ word of the EAV) and must remain valid during the entire HANC interval.                                                                                                                                                                                                                                                                                                                                        |

|            |     |       | This input is the only line number input used for SD-SDI, HD-SDI, and 3G-SDI level A modes.<br>For 3G-SDI level B mode, a second line number input port, In_b, is also provided. The line<br>numbers input on the In_a port are used only to identify the line for the purposes of inserting<br>SMPTE 352 packets.                                                                                                                                                                                                   |

|            |     |       | For video formats where the picture line number is different from the transport line number, the value supplied on this port must be the transport line number.                                                                                                                                                                                                                                                                                                                                                      |

| ln_b       | In  | 11    | This second line number input port is used only for 3G-SDI level B format. This additional line number port allows the two separate HD-SDI signals to be vertically unsynchronized when level B carries two independent HD-SDI signals. This input port has the same timing and other requirements described for In_a.                                                                                                                                                                                               |